From concept to silicon, we provide expertise for development in IP/ASIC/SOC/FPGA.

With ever increasing size of IP/SOC/ASIC and FPGA, complexity of verification is increasing exponentially. Every small change in design is resulting in long verification cycle. As a result, 50-70% of chip development resources are now getting consumed by verification efforts. With processor now part of SoC, complexity of verification further increases.

Our team has extensive experience in taking up full responsibility or being part of larger customer team, delivering module to full-chip verification for complex chips. We have worked with simple verification environment created using simple Verilog or VHDL to full coverage driven random environment in System Verilog using UVM. Our team has developed reusable Verification components from scratch as well as used industry standard VIPs as part of environment to reduce time and improve quality of verification. We have verified multiple chips, pre and post silicon, to ensure highest quality working chips.

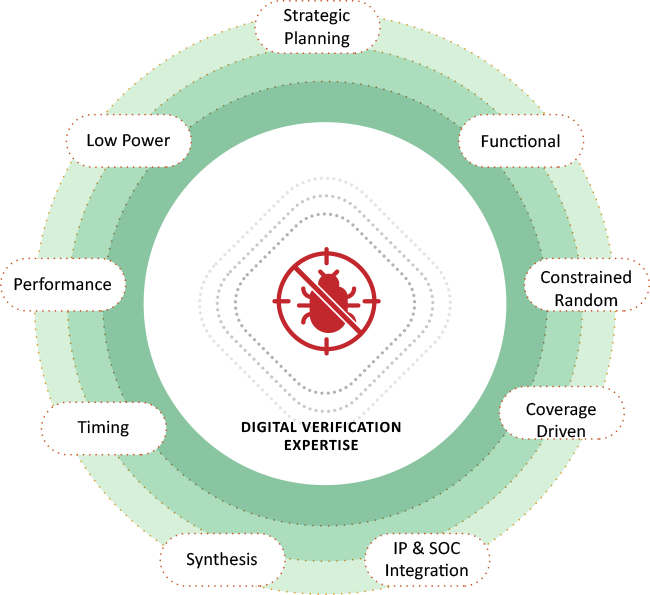

Digital Verification Expertise

- Strategic Planning

- Functional Planning

- Constrained random

- Coverage driven

- Assertion based

- Timing driven

- Performance driven

- Power driven

- Formal

- Gate level

- Post silicon